From Scripts to Super Agents: The New AI Semiconductor Workflow

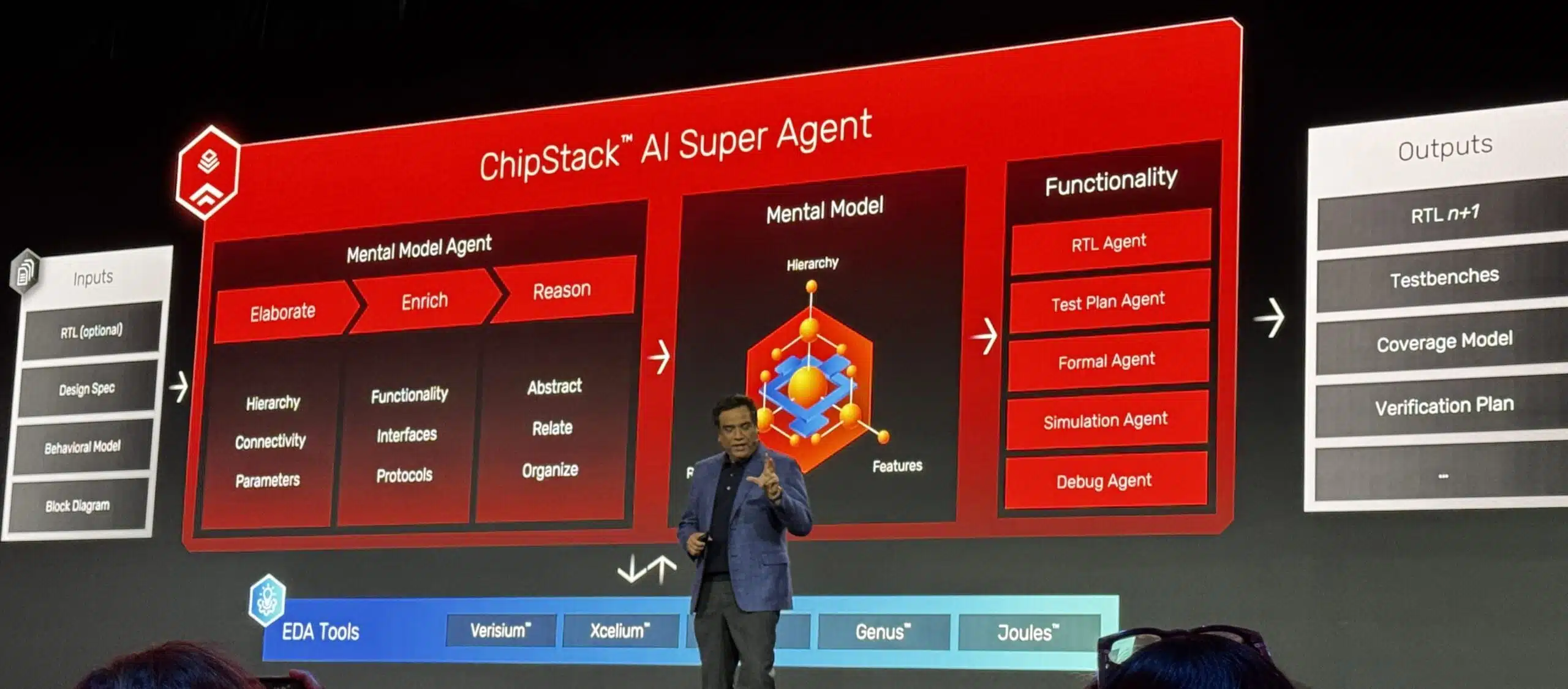

Electronic design automation used to mean scripting repetitive tasks around complex GUIs. Now, AI chip design tools from Cadence, Siemens, and Synopsys are turning those interfaces into collaborative workspaces shared with virtual engineers. Cadence’s ChipStack AI Super Agent introduced the idea of domain-specific agents that understand design intent and stay aligned through a shared “mental model” of the chip. At CadenceLIVE, the company expanded that concept with ViraStack for analog and InnoStack for digital implementation and signoff, coordinated by AgentStack into an end‑to‑end agentic flow from specification through verification. Early customers report 3–10x task‑level productivity gains, especially in the most tedious loops of drafting, checking, and fixing. Instead of manually pushing each tool in sequence, designers orchestrate multi‑step flows where AI agents handle the grunt work and surface visual diffs, constraint violations, and layout options for human review. This is what agentic AI design now looks like in practice.

Cadence’s Virtual Engineers Meet the Realities of 3D ICs

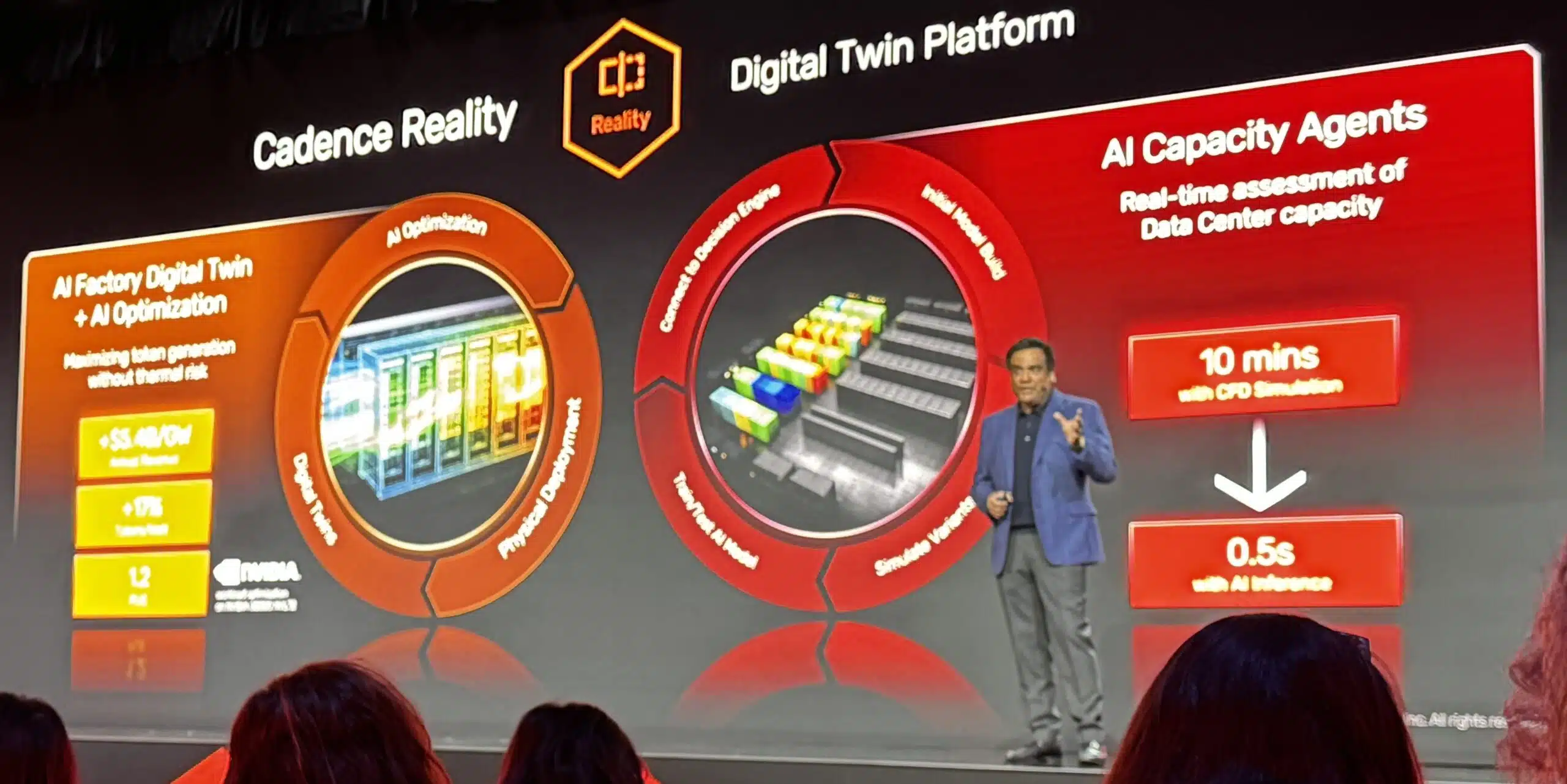

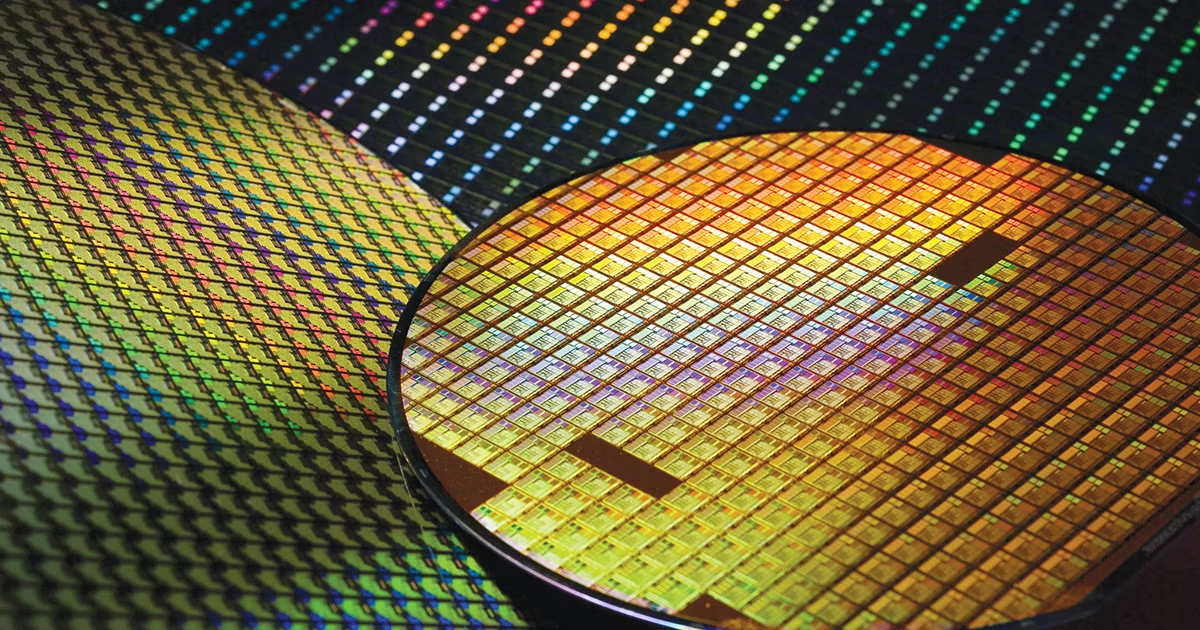

Cadence’s latest announcements highlight where agentic AI design is heading: deeply embedded inside the visual and simulation-heavy tools engineers already use. ViraStack and InnoStack sit on top of ChipStack’s mental model foundation, allowing AI agents to propose floorplans, adjust constraints, and drive verification runs while keeping context intact across the flow. CEO Anirudh Devgan singled out 3D IC signoff as one of the toughest unsolved gaps, where verification effort can dwarf design effort, especially in multi‑die packages. To attack that, Cadence is pairing its Allegro X AI packaging automation with the GPU-accelerated Millennium platform, targeting complex scenarios like CoWoS-style advanced packaging. Here the challenge is profoundly visual: agents must reason across stacked dies, interposer routes, thermal hotspots, and signal paths in 3D. Designers stay in the loop, visually inspecting AI‑generated layouts, cross‑probing simulations, and refining high‑level constraints instead of hand‑tuning every via and bump.

Siemens and TSMC: Agentic Automation Inside Familiar EDA Views

Siemens is taking a different but complementary path, embedding AI directly into established verification and implementation environments through an extended TSMC AI collaboration. At the core is the Fuse EDA AI System, a domain‑specific, agent‑based platform aimed at automating and optimizing semiconductor workflows. Working with TSMC, Siemens is using Fuse to build multi‑step, multi‑tool automations around Calibre for design rule checking and physical verification, and to accelerate digital design with its Aprisa implementation platform. Instead of replacing existing layout viewers and rule-debug dashboards, these AI agents live inside them, automatically fixing design rule violations, proposing geometry tweaks, and guiding designers through violations via visually annotated views. The partnership is explicitly focused on leading-edge process nodes, where rule decks are vast and error margins razor-thin. For engineers, this means less time tabbing between tools and more time supervising AI-generated fixes in the same interactive canvases they already trust.

Synopsys and TSMC Put AI on the Front Lines of 3D IC Automation

Synopsys’ expanded collaboration with TSMC shows how AI‑enabled analysis is becoming inseparable from layout in advanced nodes. The company is rolling out updated design software, interface IP, and analysis tools tuned for TSMC’s 3nm, 2nm, A16, and A14 processes as AI chip designs move to chiplets and advanced packaging. Its 3DIC Compiler now connects directly into RedHawk‑SC, RedHawk‑SC Electrothermal, and Ansys HFSS, letting designers evaluate power integrity, thermal behavior, and high‑speed signal quality while they manipulate 3D layouts. This is 3D IC automation in a very literal sense: AI-assisted engines trace heat paths through stacked dies, flag IR‑drop risks across chiplets, and visualize signal degradation along interconnect maps that engineers understand primarily through 3D views. Rather than manually iterating across separate tools, teams can drive constraint‑driven optimizations where AI agents propose routing, bump placement, and package configurations that close both electrical and physical requirements.

From Image Generators to Silicon: Why Creative Tech Depends on AI EDA

For creators used to AI image tools, today’s AI semiconductor workflow will feel surprisingly familiar. Agentic AI systems in chip design rely on iterative generation, constraint‑driven optimization, and rapid visual exploration—only the canvas is a 3D IC layout instead of a digital painting. Cadence’s agentic EDA vision centers on a shared design context so multiple specialized agents can collaborate without drifting from the spec, delivering quantifiable productivity gains in real projects. Siemens and Synopsys are similarly folding AI into core flows, turning verification dashboards and packaging editors into collaborative spaces for human–AI co-design. At the same time, multiphysics constraints like thermal stress, power delivery, and energy consumption are becoming first‑class design inputs as data center electricity demand climbs. The paradox is clear: the future of AI image and design tools will depend on ever more sophisticated chips, and those chips will increasingly be shaped by AI chip design tools working side‑by‑side with human engineers.